基于FPGA的HDMI显示实验的学习

🌈以下是本人对HDMI例程的学习和理解,是为了方便后续的学习,如有补充和错误,欢迎评论区留言!

1.实验设备及要求

实验设备:正点原子达芬奇开发板(Xilinx),电脑显示屏,HDMI连接线(A接口)。

实验要求:驱动FPGA开发板上的HDMI接口,在显示器上显示720p彩条图案(720p分辨率为1280*720,像素时钟大约为75MHz)。

开发环境:Vivado_2020.2、Notepad++、Visio。

2.HDMI接口(A型)简介

2.1 HDMI引脚解析

| 引脚 | 引脚类型 | 引脚 | 引脚类型 | 引脚 | 引脚类型 |

|---|---|---|---|---|---|

| 1 | 数据2+ | 2 | 数据2屏蔽 | 3 | 数据2- |

| 4 | 数据1+ | 5 | 数据1屏蔽 | 6 | 数据1- |

| 7 | 数据0+ | 8 | 数据0屏蔽 | 9 | 数据0- |

| 10 | 时钟+ | 11 | 时钟屏蔽 | 12 | 时钟- |

| 13 | CEC | 14 | 保留 | 15 | SCL |

| 16 | SDA | 17 | GND | 18 | 5V电源 |

| 19 | 热插拔 |

2.2 DVI编码输出时序

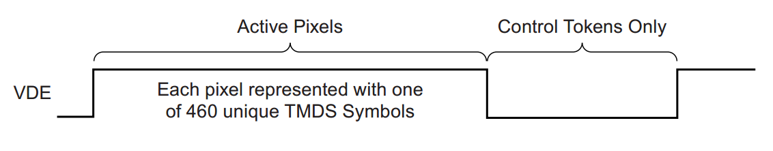

当HDMI在只使用视频传输时,它的时序逻辑等同于DVI,该编码输出时序如下:

当VDE拉高时,则传递的是图像信息,即RGB像素数据信息;而在VDE为低电平时,传递的信号是控制信号,例如行场同步信号等。

3.TMDS编码

3.1 TMDS编码介绍及作用

它的作用是对原数据加密之后通过HDMI数据线传递到接收部分进行解码,最后通过显示设备进行显示。

它适用于HDMI和DVI的视频图像的数据编码。原来的8为数据通过TMDS进行编码之后会变成10位数据,前面8位为原始数据通过异或、异或非两种方式之一得到,第9位是方式选择位,0表示通过异或非运算得到,1表示通过异或运算得到。第10位是直流平衡位,通过计算前面的0和1个数以及上冲下冲次数,最终确定第10位数据。

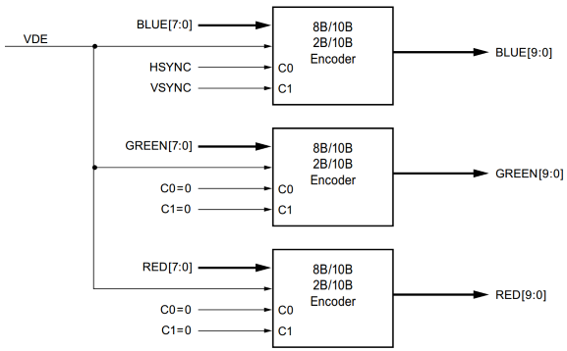

其中视频像素信息8位数据通过TMDS编码变为10位数据,而控制信号C0和C1通过查找表的形式变为10位数据。

| 参数名称 | 参数作用 |

|---|---|

| D、C1、C0、DE | D为视频信号,C为控制信号,DE为使能信号 |

| Cnt | 寄存器参数 |

| N0{X}、N1{X} | N0{X}、N1{X}图像数据中0、1的个数 |

| q_out | 编码后的输出 |

下面是完整的编码过程的流程图展示:

注:在计算机中表示负数的方式:首先取正数值的原码 —> 取原码的反码 —> 取反码的补码 —> 在符号位补1

例如负数‘-6’,6的原码是110,反码即001,补码是010,则最终‘-6’在计算机上的表示形式为1010。

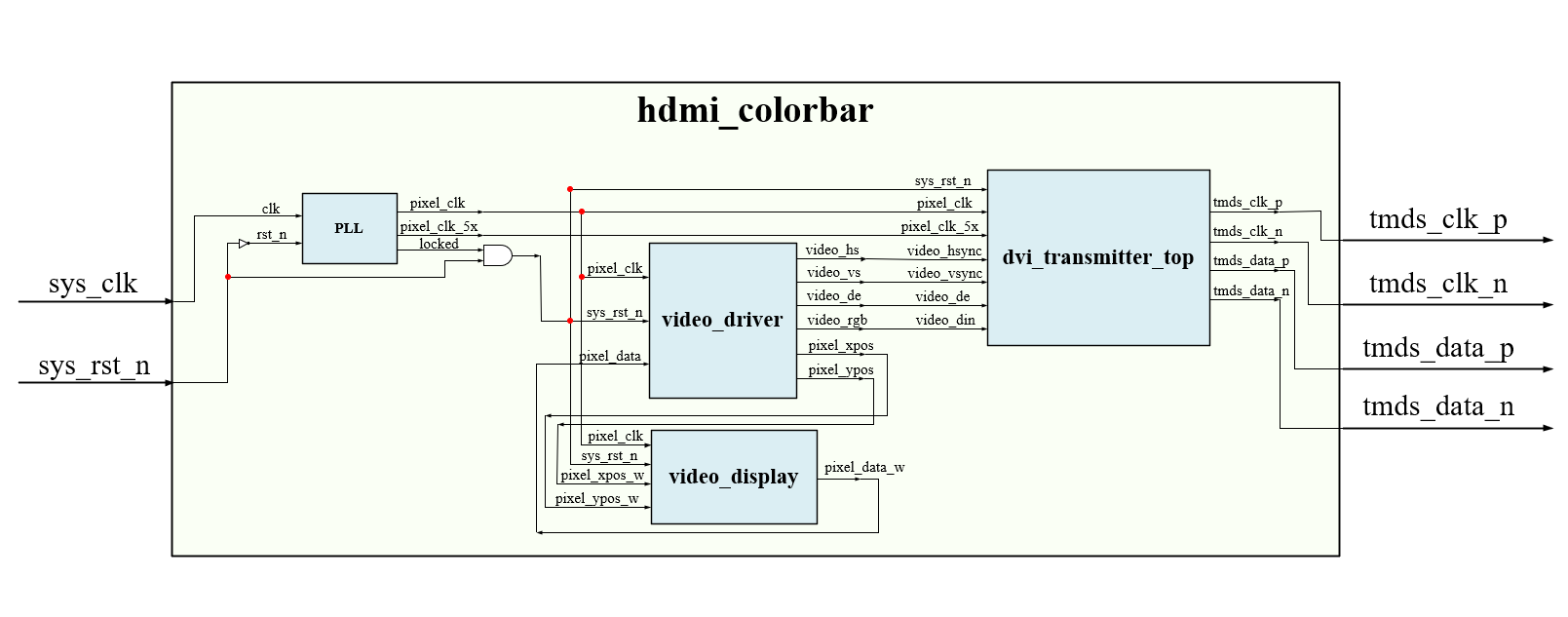

4.HDMI彩条实验代码框图及程序详解

4.1 整体模块框架

4.2 各部分模块详解

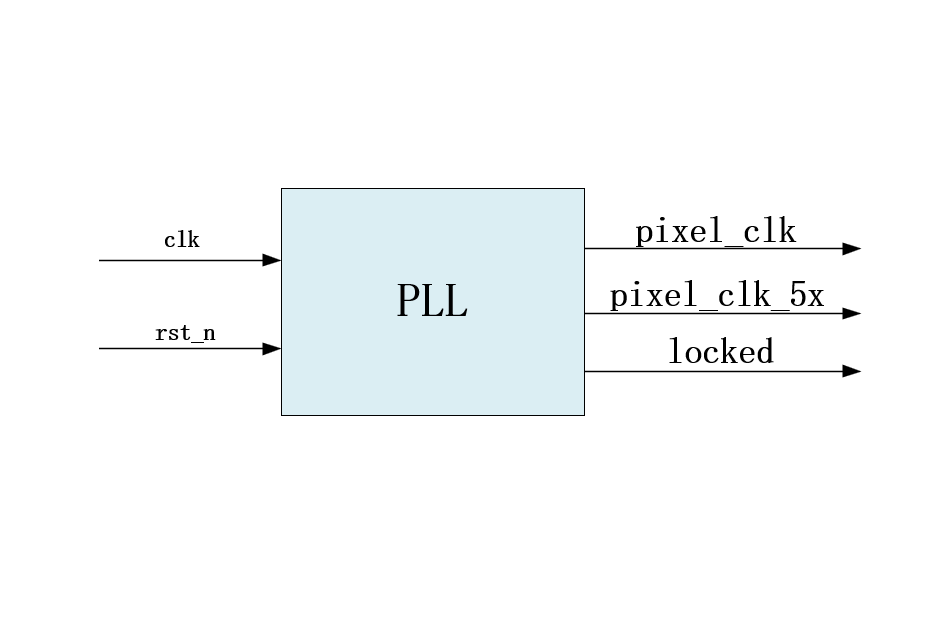

- PLL模块详解

| 引脚名称 | 引脚类型 | 引脚作用 |

|---|---|---|

| pixel_clk | output | 提供数据的传递时钟,速度为18Gbps,则时钟为75M |

| pixel_clk_5x | output | 并转串后模块的使用时钟75x5=375M |

模块作用:为后续模块提供时钟。

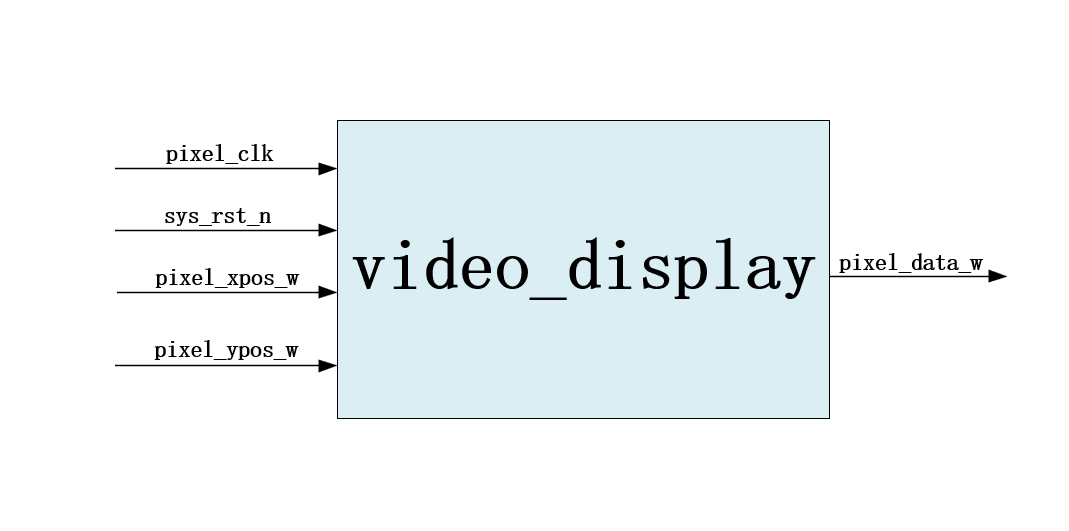

- video_display模块

| 引脚名称 | 引脚类型 | 引脚作用 |

|---|---|---|

| pixel_xpos_w | input | 当前显示位置的x坐标 |

| pixel_ypos_w | input | 当前显示位置的y坐标 |

| pixel_data_w | output | 根据上面坐标输出下一像素的数据信息 |

模块作用:根据video_drive模块提供的坐标信息,产生下一像素坐标的显示数据信息。

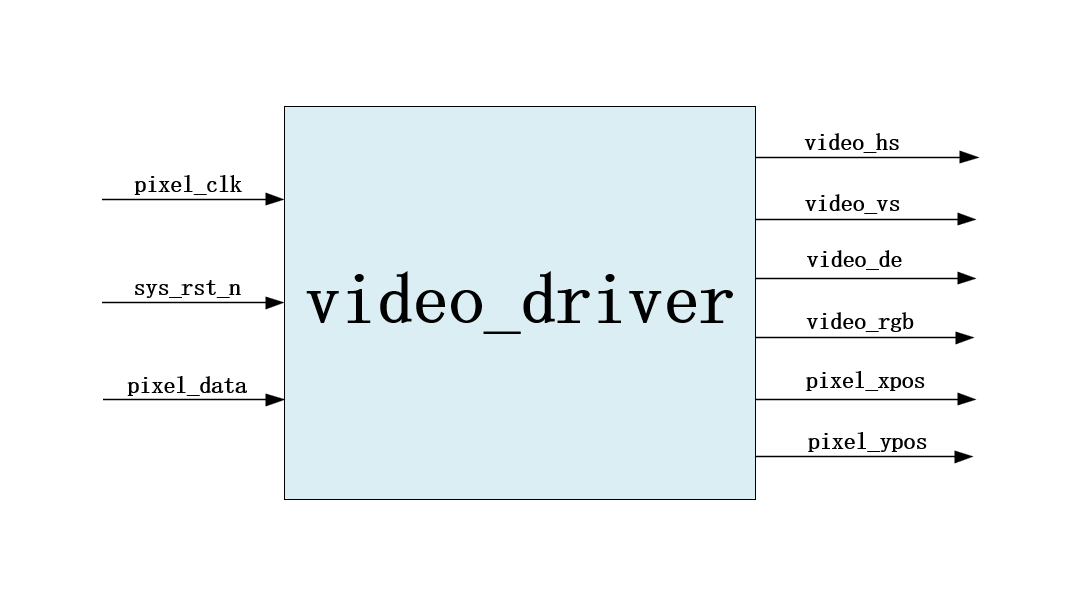

- video_drive模块

| 引脚名称 | 引脚类型 | 引脚作用 |

|---|---|---|

| pixel_data | input | 由video_display产生的video数据 |

| video_hs/video_vs | output | video的行场同步数据 |

| video_de | output | 数据使能信号 |

| video_rgb | output | 输出的像素数据,与pixel_data相同 |

| pixel_xpos | output | 显示位置的x坐标 |

| pixel_ypos | output | 显示位置的y坐标 |

模块作用:根据HDMI数据时序,产生对应信号和数据信息。

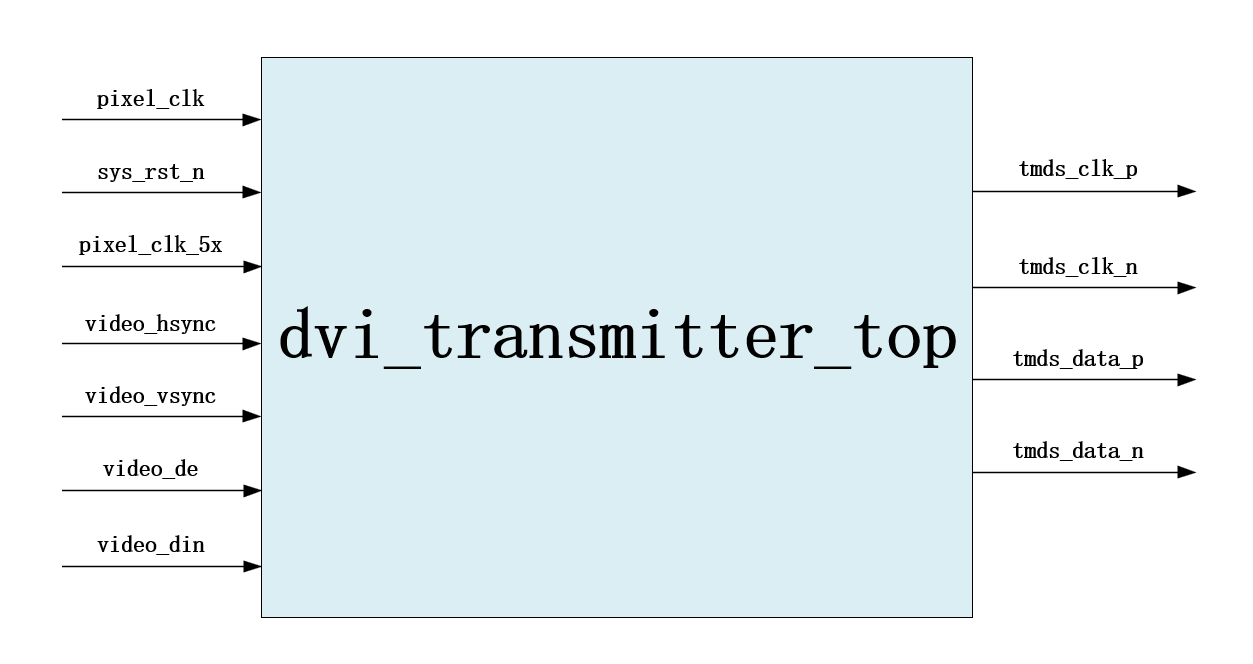

- dvi_transmitter_top模块

| 引脚名称 | 引脚类型 | 引脚作用 |

|---|---|---|

| tmds_clk_p/tmds_clk_n | out | 差分的时钟信号 |

| tmds_data_p/tmds_data_n | output | 差分的数据信号,有三路分别是R\G\B |

模块作用:对图像数据、行场同步信号、控制信号以及时钟信号进行编码、并转串以及单端转差分处理。

4.3 dvi_transmitter_top模块详解

encoder模块就是TMDS的编码模块,将8位原始数据通过TMDS编码转化为10位数据,这10位数据再通过并转串模块,即serilizer模块将10位并行数据转化为串行数据,再将串行数据TMDS模块,通过单端转差分模块,产生了差分信号。

注意:这里的时钟信号给1111100000的原因是,在pclk_5x这个时钟下输入1111100000,那么在解码时,串转并后,时钟就会变为原来的pclk。