数字锁相环中使用的IP核认识与参数配置

🌈以下主要介绍了Vivado2020.2版本下,Mult乘法器、Fir滤波器以及DDS信号发生器IP核的认识与配置。参考资料主要来源于网络及官方文档。

一.乘法器Multipiler

1.1 ip核调用

在2020.2版本中,普通乘法器所在路径如下:

Vivado Repository ----> Math Function ----> Multipilers ----> Multipiler

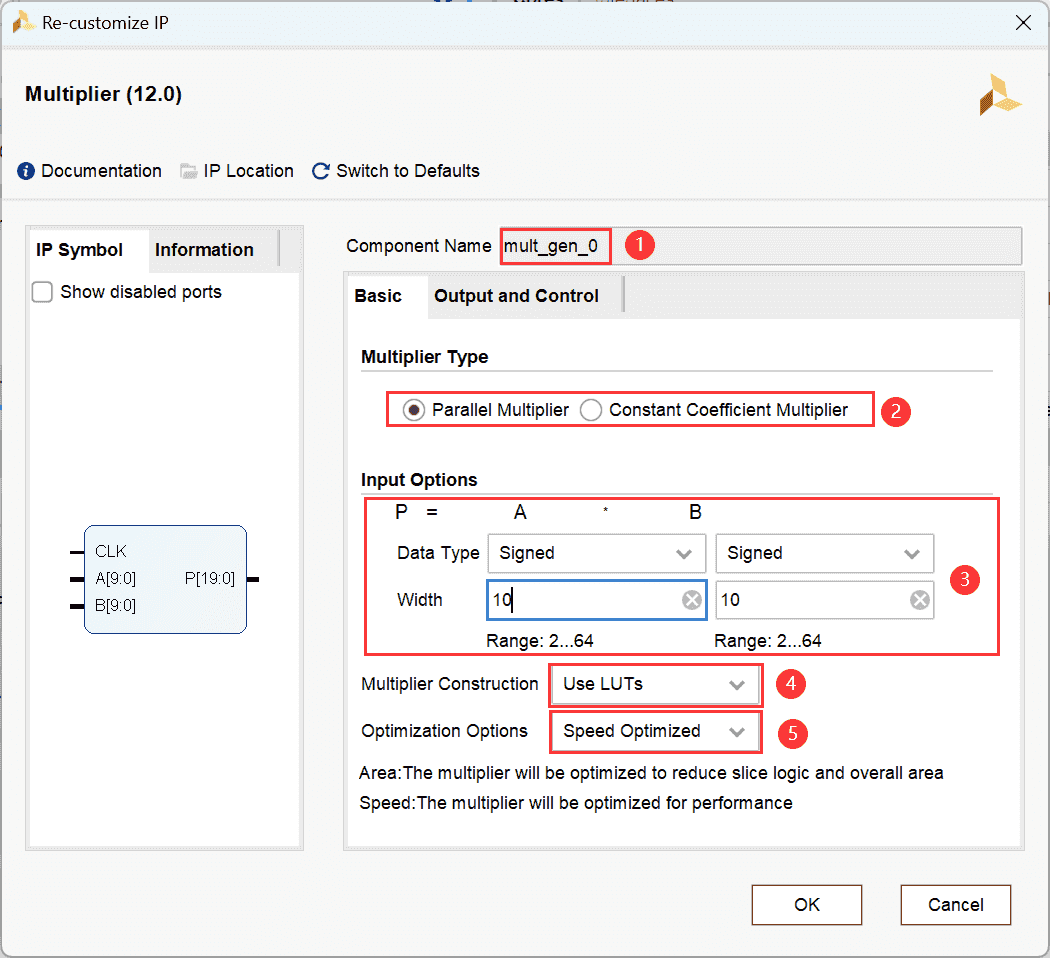

1.2 参数配置页

|

|

|---|

| 序号 | 参数作用 | 参数介绍 | 实例 |

|---|---|---|---|

| ① | 模块名称 | 自定义 | mult_gen_0 |

| ② | 乘法类型 | Parallel Multiplier:并行乘法器,即输入数据A和B可变 Constant Coefficient Multiplier:固定系数乘法器,即只有一个数据输入; |

当前A和B都可变 |

| ③ | 输入数据形式及数据位宽 | Data Type:Signed/Unsigned Width:输入数据位宽 |

有符号,数据数据位宽为10位 |

| ④ | 消耗资源类型 | Use LUTs/Use Mults | 基于查找表结构 |

| ⑤ | 优先级 | Speed/Area | 速度优先 |

| ⑥ | 输出数据位宽 | 默认即可,根据输入信号位宽 | 35位 |

| ⑦ | 时钟使能 | 高电平有效 | 使能开启 |

| ⑧ | 同步清零 | 同步清零标志位,高电平有效,正常工作为0 | 同步清零标志位开启 |

二. Fir滤波器

2.1 ip核调用

在2020.2版本中,普通乘法器所在路径如下:

Vivado Repository ----> Digital Signal Processing ----> FIR compiler

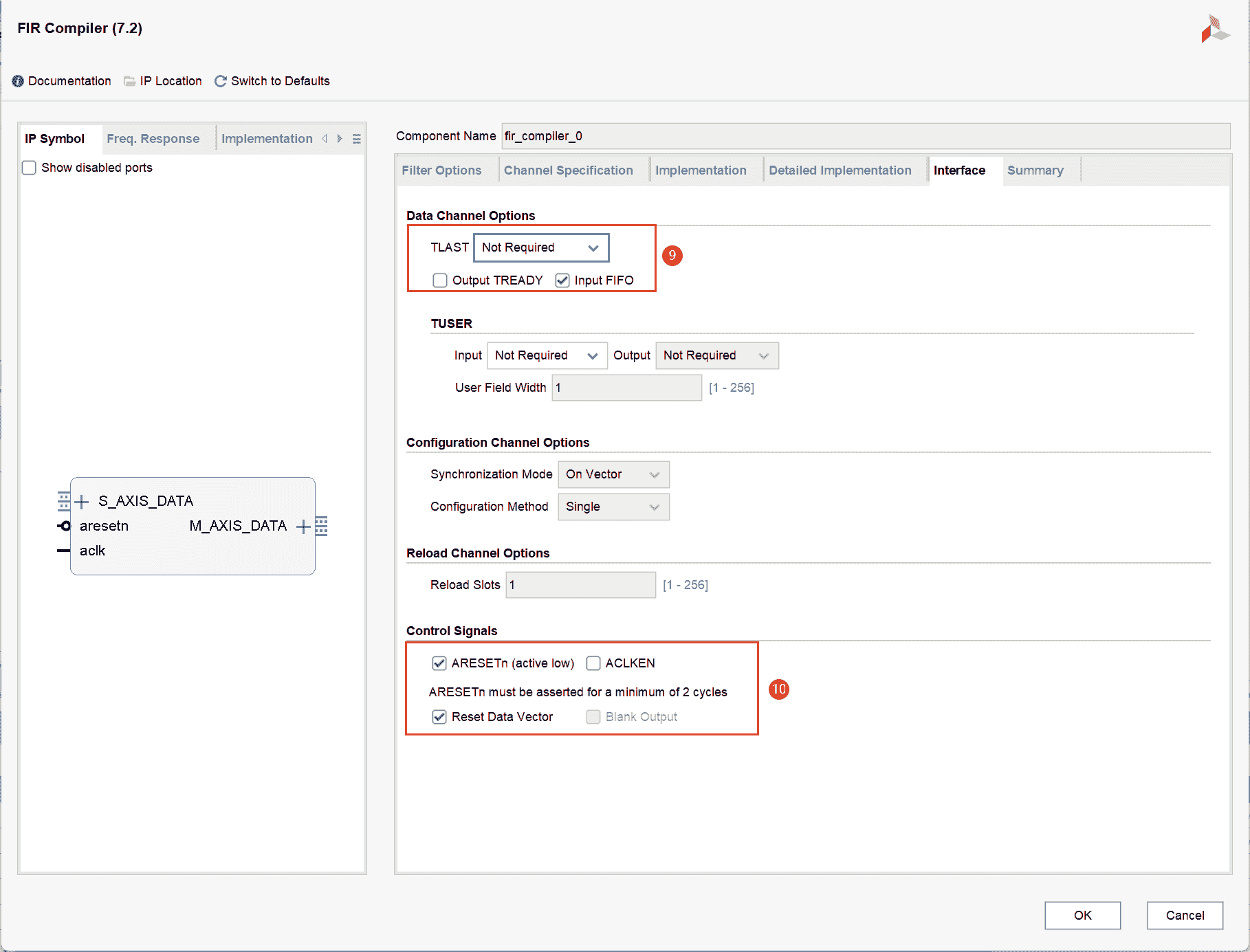

2.2 参数配置页

|

|

|---|---|

|

|

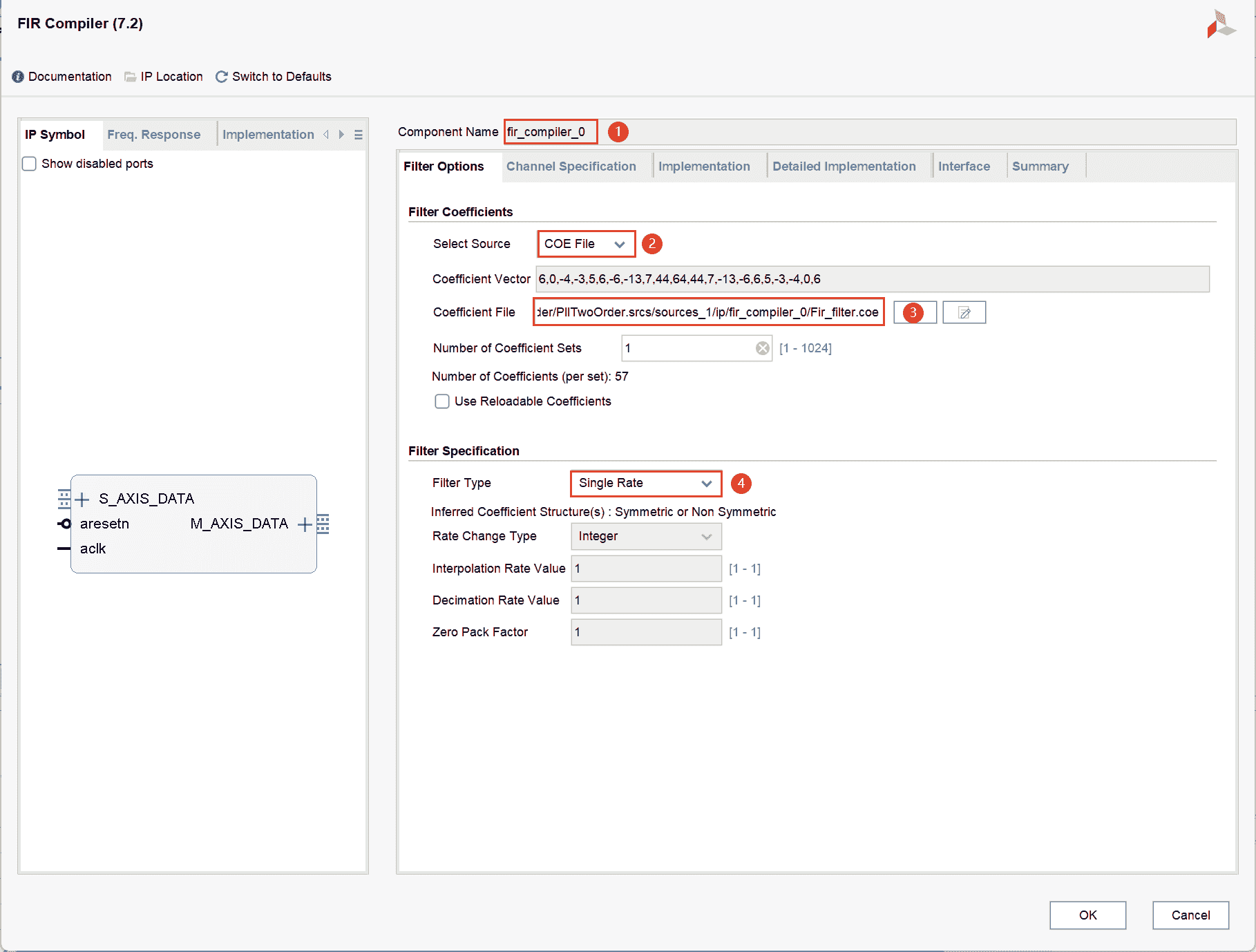

| 序号 | 参数作用 | 参数介绍 | 实例 |

|---|---|---|---|

| ① | 模块名称 | 自定义 | fir_compiler_0 |

| ② | 选择滤波器系数输入方式 | vector直接写入 / 导入.coe文件 | 导入.coe文件 |

| ③ | coe文件路径 | 文件存放路径 | d:/FPGA_Prj/PllTwoOrder/PllTwoOrder.srcs/ sources_1/ip/fir_compiler_0/Fir_filter.coe |

| ④ | 滤波器类型 | 单速率:表示输入与输出速率相同 多速率:应用于多速率信号处理,具体可参考文档 |

单速率模式 |

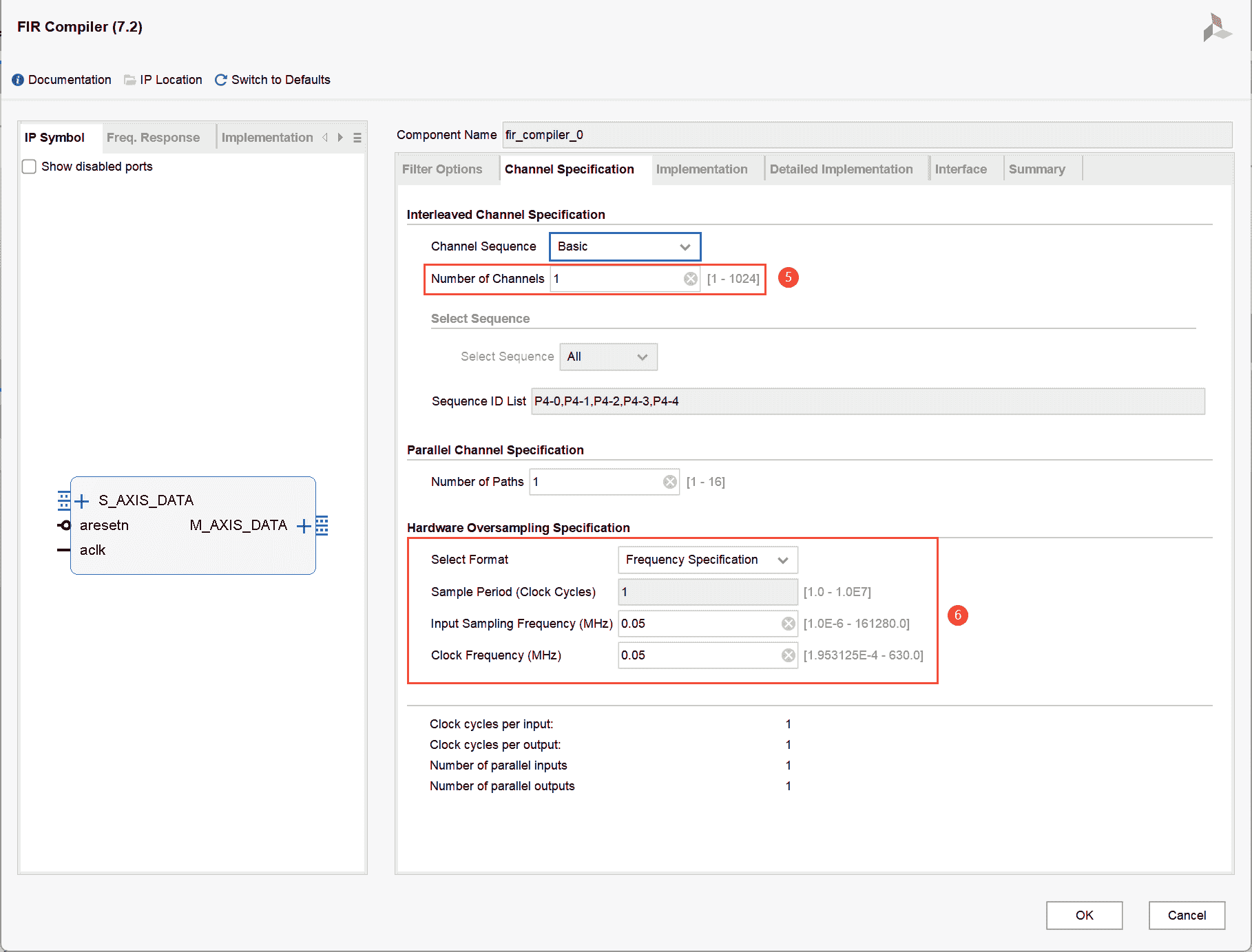

| ⑤ | 数据通道数量 | 如果设置多个数据通道的话,多通道数据通过总线接入IP核。 | 1 |

| ⑥ | 输入数据采样速率及时钟频率 | 自定义 | 50KHz/50KHz |

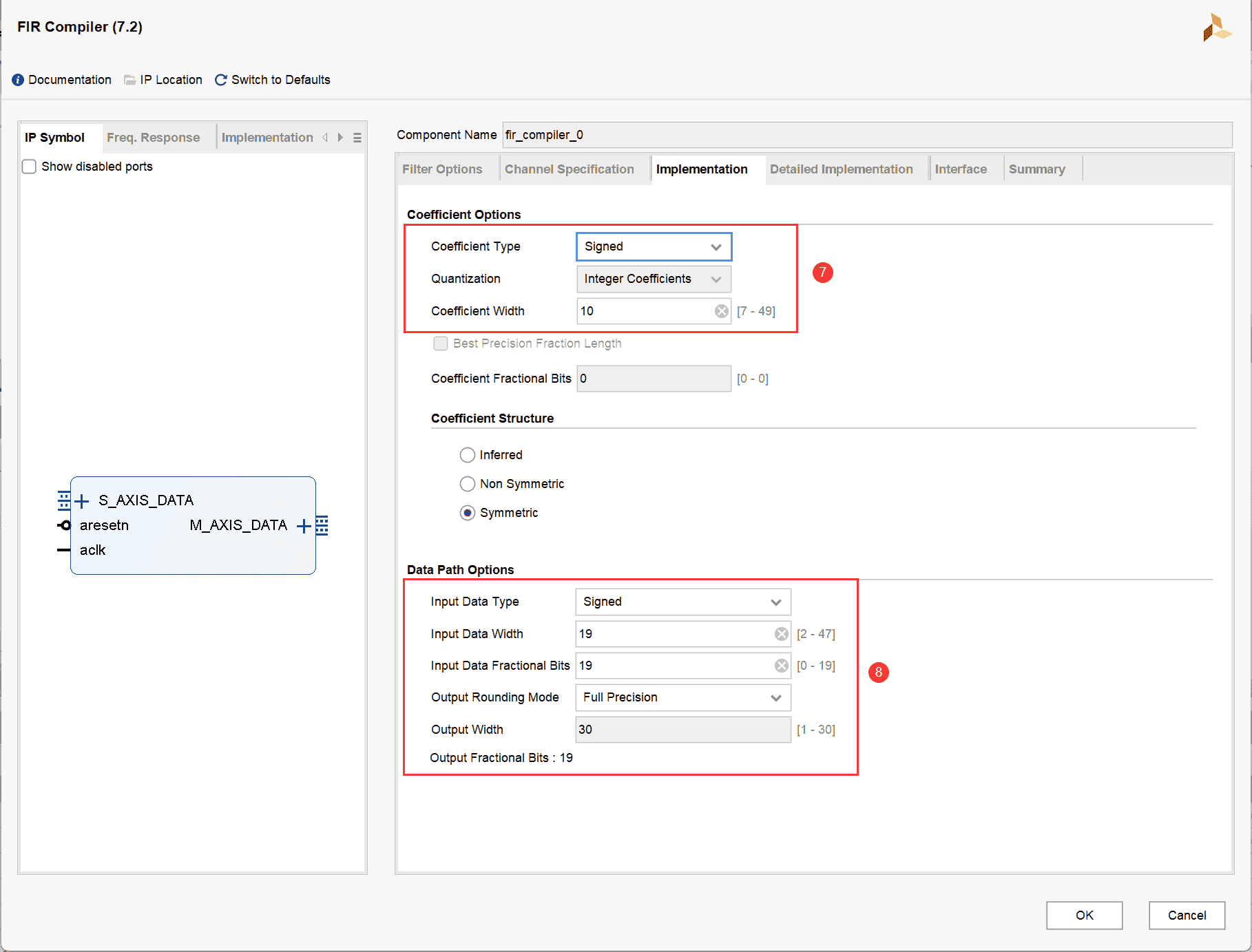

| ⑦ | 滤波器系数配置 | 选择滤波器系数为有符号数 / 无符号数、量化方法、系数位宽 | 有符号/整数系数/10位 |

| ⑧ | 输入数据配置 | 输入数据类型、位宽、小数位数、近似方式、输出位宽 | 有符号/19/19/全精度/30 |

| ⑨ | TLAST信号 | 不需要:不添加该端口 | 不需要 |

| ⑩ | 添加复位信号及时钟使能信号 | 复位信号低电平有效/时钟使能信号 | 添加/不添加 |

三.DDS信号发生器

3.1 ip核调用

在2020.2版本中,普通乘法器所在路径如下:

Vivado Repository ----> Digital Signal Processing ----> FIR compiler

3.2 参数配置页

评论